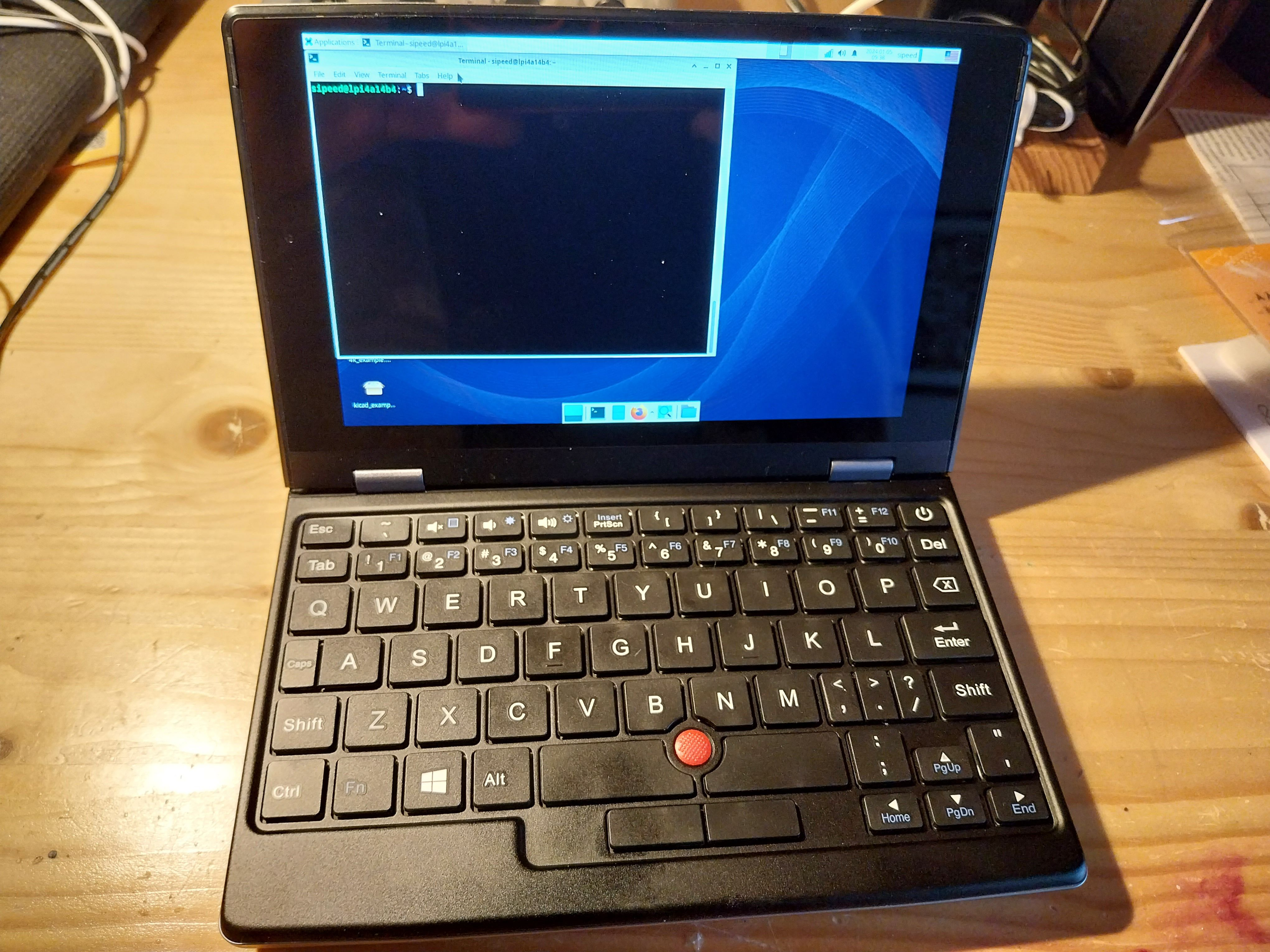

RISCV Lichee Console 4A mini laptop discovery

For my experimentation, I’ve access to a Lichee Console 4A minilaptop which, to my knowledge is the first laptop based on RISC-V technology. It’s not exactly a usual laptop, the denomination is “Portable RISC-V Development Terminal”. It’s build by Sipeed https://sipeed.com/licheepi4a and sell on aliexpress https://fr.aliexpress.com/item/1005006174268912.html

Since it’s based on RISC-V architecture we can have many documentations:

-

Technical, on the chip itself: https://wiki.sipeed.com/hardware/en/lichee/th1520/lp4a.html

-

With a scientific description https://ftp.libre-soc.org/466100a052.pdf

-

On the mother board : https://dl.sipeed.com/shareURL/LICHEE/licheepi4a

The machine come with a preinstalled linux installation :

lpi4a14b4:~/tmp/>lsb_release -a

No LSB modules are available.

Distributor ID: Debian

Description: Debian GNU/Linux 12 (bookworm)

Release: 12

Codename: bookworm

lpi4a14b4:~/tmp/>uname -a

Linux lpi4a14b4 5.10.113+ #1 SMP PREEMPT Fri Dec 15 09:57:23 CST 2023 riscv64 GNU/Linux

The graphical system is based on xfce4, and is quite responsive.

The core processor is a RISC-V 64 bits, 4 cores, with many extensions :

processor : 3

hart : 3

isa : rv64imafdcvsu

mmu : sv39

cpu-freq : 1.848Ghz

cpu-icache : 64KB

cpu-dcache : 64KB

cpu-l2cache : 1MB

cpu-tlb : 1024 4-ways

cpu-cacheline : 64Bytes

cpu-vector : 0.7.1

The rv64imafdcvsu should be interpreded as (https://en.wikipedia.org/wiki/RISC-V)

-

RV64I Base Integer Instruction Set, 64-bit

-

M : Standard Extension for Integer Multiplication and Division

-

A : Standard Extension for Atomic Instructions

-

F & D : Standard Extension for Single & Double -Precision Floating-Point

-

C : Standard Extension for Compressed Instructions (16 bits for common instructions)

-

V : Standard Extension for Vector Operations

-

S : Standard Extension for Supervisor-level Instructions

I’ll certainly publish more testing on this machine in a near future.