Recrutement étudiant en thèse "Micro-compilation pour réseaux de neurones ternaires sur une architecture de calcul proche mémoire"

L’Intelligence Artificielle et le Computer Vision sont désormais massivement déployés au plus proche capteur de façon à permettre d’étendre les capacités des systèmes d’imagerie embarqués. Les récentes avancées en Deep Learning démontrent que les réseaux de neurones fortement quantifiés (dont les poids et les activations sont représentables sur peu de bits) tendent à égaler leurs homologues non quantifiés en termes de performances en inférence pour des tâches allant de la détection ou reconnaissance d’objet au débruitage et à la compression vidéo. Or l’usage d’une arithmétique réduite a l’avantage de pouvoir exploiter au mieux les architectures de type In-Memory Computing (IMC).

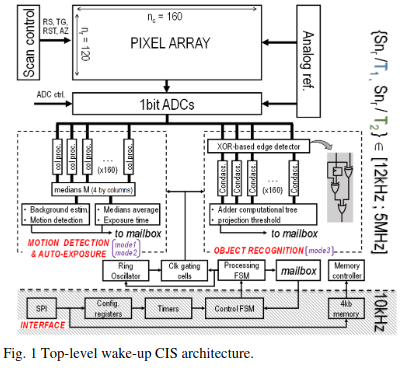

Exemple d’un design conjoint algo/archi pour un capteur d’image autonome (exrait de https://doi.org/10.1109/VLSICircuits18222.2020.9162854 )

L’adéquation algorithme/architecture réalisée à l’aide d’une combinaison de fonctions logiques massivement parallélisées avec des opérateurs de calculs analogiques dédiés permet typiquement un gain énergétique de plusieurs ordres de grandeur par rapport à une approche conventionnelle. En s’appuyant sur de récents travaux menés au CEA relatifs aux accélérateurs matériels pour effectuer de l’inférence proche imageur très basse consomation, ce projet de thèse vise à mettre au point un modèle de programmation innovant spécifique à ce type d’architecture dont l’objectif est de permettre un haut niveau de reconfigurabilité de la topologie du réseau de neurones déployé, en fonction des besoins de façon à permettre une plus grande plage d’applications en vision. Pour profiter au maximum de la parallélisation des opérations de calculs en limitant les coûts d’accès mémoire, le compilateur à concevoir aura la tâche d’optimiser au mieux le séquençage et la répartition des calculs.

La thèse sera co-encadrée par William Guicquero et moi-même (Henri-Pierre.Charles@cea.fr ). Nous contacter pour plus de détail, sinon le lien pour les candidatures est à la fin de ce message

- Les étapes principales de la thèse seront les suivantes :

- Étude bibliographique et prise en main des concepts de réseaux de neurones quantifiés dans le contexte du traitement d’image.

- Maitrise des outils d’analyse permettant de générer automatiquement des graphes de calculs.

- Identification des possibles organisations de données et des routines de calculs adaptées à l’IMC.

- Développement et programmation du compilateur dédié et du simulateur hardware associé.

Site pour la candidature : https://instn.cea.fr/these/micro-compilation-pour-reseaux-de-neurones-ternaires-sur-une-architecture-de-calcul-proche-memoire/