Soutenance de thèse : Unification des mémoires réparties dans les systèmes hétérogènes

Erwan Lenormand soutiendra sa thèse intitulée “Unification des mémoires réparties dans les systèmes hétérogènes” le lundi 31 Janvier 2022 à 14h dans les locaux de NanoInnov, Bâtiment 862 - Amphi 33 - 2 Bd Thomas Gobert, 91120 Palaiseau, France

Teaser : quel rapport entre les accélérateurs FPGA, les mémoires distribuées, la simulation de tsunamis et les courbes de Hilbert ?

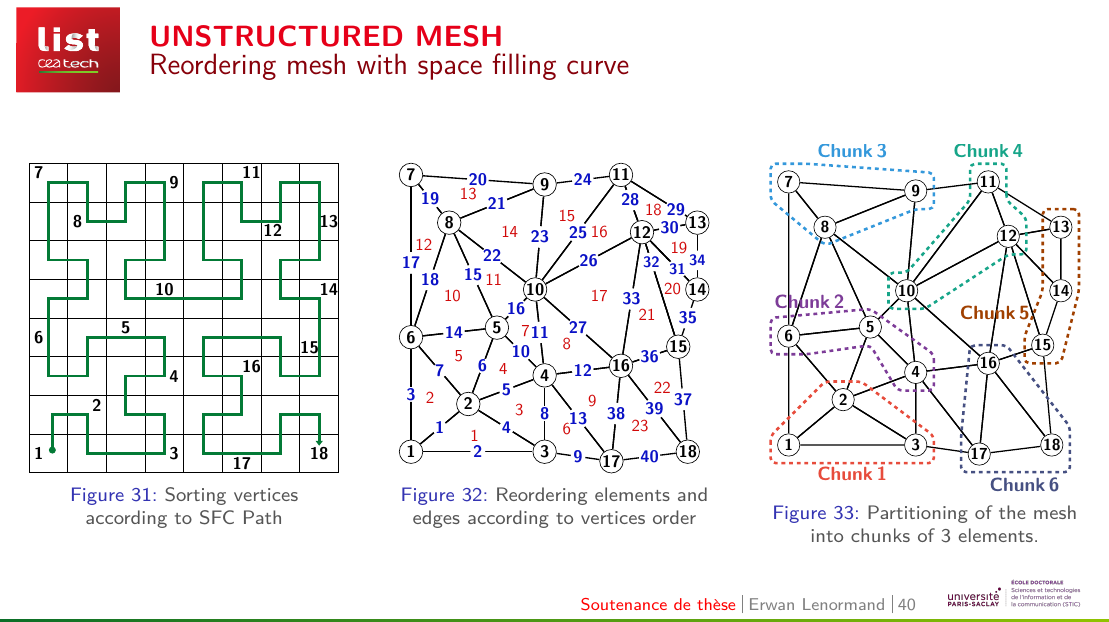

Utilisation d’une courbe de PEANO pour améliorer la localité spatiale des données accédées par un accélérateur FPGA

Le jury sera constitué de

- Monsieur Samuel THIBAULT Professeur Rapporteur

- Monsieur Tanguy RISSET Professeur Rapporteur

- Monsieur Marc PERACHE Directeur Examinateur

- Madame Soraya ZERTAL Maître de conférences Examinatrice

- Monsieur Olivier MULLER Maître de conférences Examinateur

- Madame DEZAN CATHERINE Maître de conférences Examinatrice

- Monsieur Henri-Pierre CHARLES Directeur de recherche Directeur de thèse

- Les co-encadrants sont MM Loic CUDENNEC, Thierry GOUBIER et Stéphane LOUISE

Résumé : Suite à la perte de la mise à l’échelle de Dennard, les systèmes de calcul de- viennent de plus en plus hétérogènes, notamment par l’ajout de coprocesseurs. Grâce à leur architecture optimisée pour traiter massivement les données, les coprocesseurs permettent à la fois d’accélérer le traitement des applications et d’en augmenter l’efficacité énergétique. Cependant, cette amélioration des performances par l’hétérogénéité se paie au prix d’un modèle de programmation hybride et distribué rendant l’utilisation des systèmes plus complexe. Cette thèse souhaite adresser le problème de la gestion des données dans les systèmes hétérogènes. Beaucoup d’approches ont été proposées pour répondre à cette problématique. Si elles présentent toutes des caractéristiques différentes, la majorité repose sur un partitionnement à gros grains des structures de données en blocs réguliers. Les blocs sont transférés avant le lancement des noyaux de calcul pour satisfaire les dépendances de données. Ces approches permettent de gérer efficacement des structures de données régulières dont le traitement génère des motifs d’accès réguliers et prévisibles. Cependant les applications de calcul utilisent de plus en plus des structures de données irrégulières dont le traitement provoquent des accès aléatoires et imprévisibles. Tel que l’illustre le banc de test High performance Conjugate Gradient, les performances de ces applications sont limitées par celles des systèmes mémoires et d’interconnexions. Ainsi, l’optimisation de ces applications nécessitent de limiter les échanges de données entre les différentes mémoires. Une mémoire partagée offre un paradigme pratique pour la programmation de ce genre d’applications en résolvant les problématiques de la localisation, de l’orchestration des transferts et du maintient de la cohérence des données. Grâce à leur architecture programmable, les accélérateurs reconfigurables semblent être les ressources de calcul les plus adaptées pour traiter les applications irrégulières. Ainsi, dans le cadre des travaux de cette thèse, nous avons proposé d’étudier l’intégration d’accélérateurs reconfigurables dans une Mémoire Virtuellement Partagée (MVP). Ce positionnement se distingue de l’état de l’art par la capacité donnée aux accélérateurs d’initier les accès aux données distantes. Pour ce faire, nous avons proposé un modèle d’intégration des accélérateurs dans une MVP logicielle déjà existante. Cette intégration repose sur un système de proxy permettant de faire communiquer les noyaux de calcul, implémentés sur la logique programmable de l’accélérateur, avec l’environnement logiciel de la MVP. Nous avons proposé un modèle de programmation pour ce système qui répond aux besoins des applications dont les motifs d’accès aux données sont aléatoires. Pour résoudre le problème de la latence d’accès aux données dis- tante, le modèle de programmation utilise la superposition temporelle des flux de données transférées avec les flux de données traitées. Pour ce faire, il s’appuie sur un partitionnement des structures de données irrégulières en blocs de tailles adaptables permettant de masquer l’irrégularité des structures et de précharger les données sous forme de flux réguliers. Nous avons développé un outil de modélisation et de simulation permettant de valider le système et le modèle de programmation proposés. Deux cas d’études, la multiplication de matrices creuses et un code de simulation de tsunami, ont été utilisés pour mener les expérimentations. Ils ont permis d’évaluer le modèle de programmation pour deux structures de données irrégulières largement utilisées : les matrices creuses compressées et les maillages non structurés. Les résultats obtenus ont montré que le modèle de programmation permet de cacher efficacement les latences d’accès aux données et de quasiment atteindre les performances maximales permises par la bande passante du système mémoire du FPGA modélisé.