Instruction Set Design Methodology for In-Memory Computing through QEMU-based System Emulator

We (Kevin Mambu, Julie Dumas, Henri-Pierre Charles, Maha Kooli) have published a new article during the 32nd International Workshop on Rapid System Prototyping (RSP) during ESWEEK. This article explains how we experiment our compilation chain for In Memory Computing platform using the QEMU emulator and a performance model.

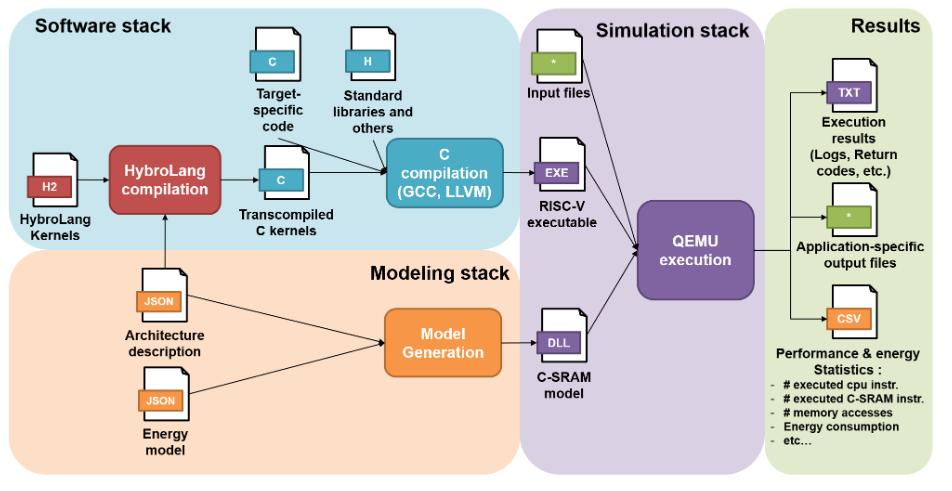

Proposed compilation & simulation flow: software stack allowing the code generation using HybroGen compilation environment & HybroLang programming language presented in [13], modeling stack representing C- SRAM architecture, simulation stack representing the QEMU-based propose platform, and results giving statistics regarding energy and performance.

All the details are on the HAL article and on the ACM platform in a near future.

Abstract : In-Memory Computing (IMC) is a promising paradigm to mitigate the von Neumann bottleneck. However its evaluation on complete applications in the context of full-scale systems is limited by the complexity of simulation frameworks as well is the disjunction between hardware exploration and compiler support. This paper proposes a global exploration flow in the scale of Instruction Set Architectures (ISA) to perform both modeling and the generation of compiler support to perform ISA-level exploration. Our emulation methodology is based on QEMU, implements a performance model based on hardware characterizations from the State-of-the-Art, and allows the modeling of cache hierarchies, while our compiler support is automatically generated and based on a specialized compiler. We evaluate three applications in the domains of image processing and linear algebra on a reference IMC architecture, and analyze the obtained results to validate our methodology.